|

高周波部のブロックダイアグラムを下記に示します。

回路図はこちら ページ1 (PLL・デジタル)

ページ2 (受信ユニット)

ページ3 (Mixer回路)

ページ4 (送信ユニット)

ページ5 (スイッチ・外部I/F)

1. IF周波数のについて

受信部は、ダブルスーパーとし、手に入れやすいクリスタルの周波数に合わせたため、1st中間周波数を4551KHzと2ndを455KHzにしました。つまり、4551-455=4096KHzのクリスタルはデジタル用の物が市場に出回っているためです。50.600MHzを運用の中心と考えると、50600-4551=46.049MHzが1st局発ということにまります。

2. 利得配分について

中間周波数を選ぶのと同様に重要なのが、各ステージでの利得配分です。これが悪いと、十分な感度やパワーが得られなかったり、不必要な回路で発振をしてしまうことがあります。

受信部: 前記の「メーカー製リグの実力」から-110dBm以下で十分なS/Nが得られることを目標としました。しかし、LA1600の実力がよくわからなかったため、2ndMixer以降のステージを事前に作成して、その実力を試しました。試行錯誤から、-90dBm程度が限界らしいことがわかり、余裕をみて+30dBをその前段で稼ぐように設計することにしました。

送信部: 送信パワーを1Wとしたため、3ステージで構成しました。 2SC1906のプリドライバーで20mW(+13dBm)に、ドライバーで0.25W、ファイナルで1W+α(1.2W程度)を得ています。一度でもTRでC級アンプを作ったことがある方ならおわかりでしょうが、所定の入力電力がないと、そのステージの出力はまったく出てきません。何か、スイッチング回路を作っている感覚になります。ドライバ段の2SC2086はそのデータシートにあるように、20mWを、ファイナルの2SC1974には0.15〜0.2Wを入れて初めてパワーが出てきます。

3. PLL回路の設計

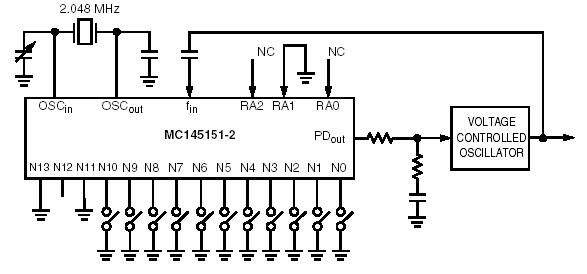

広い送受信周波数範囲、周波数の直読、及びトランシーブ操作を可能とするため、PLLを使うことにしました。AMということもあり、分解能は1KHzの分解能(ステップ)が必要と思います。今回は以前ハムフェアで手に入れたモトローラのMC145151を使用しています。ちなみに、このICは現行品のようで、モトローラーのWebから資料が取れました。(2006/11現在)メーカサンプルなどで入手できるようです。このICは、PLLICの中では、非常にシンプルな構成です。余談ですが、通常は送信用・受信用の回路が別(デュアル)で、且つ、VCOの周波数を分周するプリスケーラまで搭載しているものがあります。

回路図を見ると複雑ですが、IC周辺は次のような動作をしています。

この回路だけで、運用周波数:50.600MHzを例に取ると、受信時の46.049MHzと送信時の50.600MHzをVCO(Voltage Controlled Oscillator)で得られればよいのですが、このICの上限が25MHz(25℃時)であることと、ステップ数を1KHzとするため、PLL回路は低い周波数で動作させる必要があります。そこで、36MHzのオシレータを別途用意し、このVCO出力とMixして所定の周波数を得ています。

一方、このICのRA0−RA2の論理で、比較周波数を決めています。

| 送受信周波数 |

送信時 VCO出力 |

PLLIC 分周比 |

受信時 VCO出力 |

PLLIC 分周比 |

| 50.400MHz |

14.400MHz |

14400 |

9.849MHz |

9849 |

| 50.600MHz |

14.600MHz |

14600 |

10.049MHz |

10049 |

| 50.800MHz |

14.800MHz |

14800 |

10.249MHz |

10249 |

PLLICの分周比はバイナリーコードにしてN13−N0の論理に反映させます。例えば、14.600MHz送信時には14600分周で「11100100001000」の論理とします。 これを、後述するPICマイコンからタイムリーにコントロールします。

当然のことながら、VCOは受信時の最低周波数9.849MHzから送信時最高周波数の14.8MHzの少なくとも4.951MHzの発振範囲が必要です。実は、この発振範囲を得るためにかなり苦労しました。当初、この回路はPICマイコンとのIFのために5Vの回路としたかったのですが、VCOのバリキャップに加える制御電圧(PDout)が不足して発振範囲が狭く、送信/受信が両立しませんでした。回路定数をいじって、 ICの動作電圧を8Vまで高めて、何とか範囲に収めることが出来ましたが、8Vを作る回路やPIC

IC(実際にはHC164)間で電圧レベルを変換が必要になってしまいました。

4. 使用部品について

変調部

AFアンプそのものは自作の世界では30年前から使われているNS社のLM380Nと、前段に一石マイクアンプをつけたシンプルな構成です。これを変調トランスST-41に入れ、ドライバー段とファイナルをコレクタ変調しています。

送信回路

三菱2SC2086を使っています。元々、27MHzのCB用の石ですので、今回のようなAM機にはうってつけです。ファイナルの松下製2SC1974は既に保守品ですが、名古屋の半導体店に売られていました。当初は三洋の2SC2078を使用予定でしたが、こちらでは入手できませんでした。(サトー電気などで入手可)特性的にはよく似ています。

初段RF回路

デュアルゲートの3SK183で20dBのゲインがあります。 この石にした理由は、単純に名古屋・大須の某半導体ショップでたまたま持っていたという理由です。残念ながら、日に日にこの手の半導体は入手が困難になっています。「その時、入手できる部品をいかに使うか?」が今後の自作のキーポイントの一つである気がします。

1stMixer

2SK241のデュアルです。結構苦労したのが、この回路。出力の歪みを最小に且つ、変換利得(+10dB)を得るため、最終的にこの回路構成にしました。

2nd IF

2ndOSC用のクリスタルの入手の問題から、これを4069KHzとし、4551KHzに1stIFを設定。

2ndMixer, IF, DET

前記したように、三洋のラジオ用IC、LA1600を使用しています。これを使用した製作記事は多く見られますので、石の詳細はそちらにゆずります。ここで、迷ったのが455Khzのセラミックフィルタです。ここでは村田の「CFU455F2」という6KHz帯域のものにしました。「切れ」はこんなものか?というレベルです。当初はラダー型のクリスタルフィルタも考えたのですが、入手できるクリスタルの周波数にIFなどを合わせる手間や、今の6mAMの現状を考えると「QRMが起こるほど局がいるのか?」等からの結論です。

|