| 製作ポリシー・過程 |

| ■ Mk-94製作ポリシー |

| ■ 部品の入手 |

| ■ 問題点対策 |

| ■ 本機の運用実績 |

| 回路とソフトウエア |

| ■ クリスタルフィルタ |

| ■ PLLとDDSのコラボ |

| ■ PICマイコンの限界 |

| ■ 受信部の各ステージ |

| ■ 送信部の各ステージ |

| 資料室 |

| ■ 図面関係 |

| ■ プロフィール |

Top |

| PLLとDDSのコラボレーション |

|

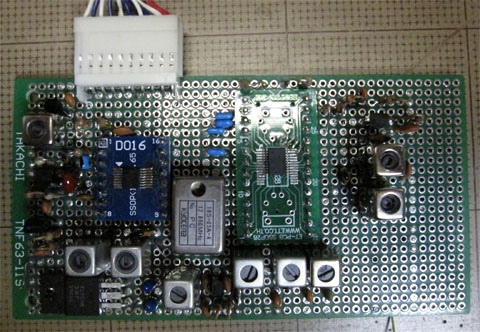

このブロックでは、IFの6MHzとミックスさせて、50MHzを生成(TX),又は50MHzから6MHzに変換するために44MHz台のVFOになる必要があります。正確には、44.000−44.700MHzを100Hzステップ(切り替えにより1KHz/10KHzステップ)で発振させることを目指します。

いくつかの紆余曲折を経て、下記のような構成に落ち着きました。

<構成>

PLLICはTC9256P(東芝)としました。一応「現行品(2010年12月現在)」ですが、「新規設計に適さず」とマニュアルに記載があります。既に「古いIC」の部類ですが、このICは、AM/FMチューナーのPLLICとして、結構自作派には人気があるICのようで、Webにも製作記が多数アップされています。しかし、入手はどこの半導体店でも置いているわけではなく、通販(e-ere)で購入しました。

データはシリアル入力で、PIC(DSP側)より、PE/CLK/DATAで転送されます。FM放送周波数まで使用できるということで、1/2のプリスケーラまで持っています(今回は使っていません)

比較周波数は50KHzとしました。9256Pは1KHzから100KHzまで、選べるようですが「なるべく比較周波数を高めたほうがCN値に有利」というセオリで、この値としました。

よって、このPLLでのステップは50KHzごとになりますが、SSB/CW機において、このステップでは使い物になりません。そこで、その間の偏移をDDSで変化させる設計です。

PLLは、VCOでの発振周波数をIC内で比較周波数まで分周し、一方「基準周波数」というものを準備し、これも比較周波数まで分周し、お互いを比較して、その差異を信号化してLPFにおくります。この基準周波数、普通はクリスタルによる固定値にするのですが、ここにDDSからの波を入れてやります。

TC9256Pでは、基準周波数を幾つか選ぶことができるのですが、Typ値では4.5MHzのようですので、DDSでこの値から50KHzを変化、つまり4.500から4.550MHzまでをPLLICに入力します。この50KHzの間を、DDSの分周比を変化させることで、100Hzステップを実現しようというものです。

<TCXOについて>

昨今の現在のメーカー製リグでは、これもあたりまえのことですが、DDSの原発にはTCXO(温度補正型クリスタルオシレータ)を使います。性能は抜群で、回路をドライヤーやQレイであぶったり冷やしたりしても、10Hzずれるかどうか?というレベルです。もちろん、常温でほっておいても、1Hzの値が変化する程度(これも、周波数カウンタ側の偏差かもしれない)です

逆に、大きなデメリットとして、アマチュアが入手できるものは限られるので、「入手できるものをどう使うか?」というスタンスで設計しないといけない点です。今回は、秋月電子の通販で入手できたKYOCERA製の12.8MHzのものを使いました。 <発振回路+フィルタ>

VCOの発振は一般的なクラップ回路+アンプですが、スプリアスが大きく、出力にはLPFとBPFをシリーズに入れています。LPFで、2倍波・3倍波を減衰。BPFでは、DDSを使うことで起きる6MHzの両サイド(44±6MHz波)をカットしています。

また、真鍮板を半田付けしてキャビティを作って、基板をその中に入れて安定化を図っています。 <ADF4110での失敗> 実のところ、当初の計画ではADF4110というアナログデバイス製のPLLICを使おうとしました。このPCは携帯電話やGSMモデム用のPLLICで、550MHzまで使用できて、チップもSSOPという非常に小さいもので、言ってみれば「今時のIC」です。

サンプルとしてメーカから入手後、回路もプログラムも組んで、44MHzを発振させ、色々試みたのですが、どうしても「ジッターノイズが取れない」ということで断念しました。

原因は基準発振器の周波数が低すぎることと、このICにおける「入力波形」の制限でした。

前記したように、DDSに入れるTCXOが12.8MHzであるため、6MHz近くがDDS周波数の限界で、その関係で当初は5MHzを用意し、ADF4110に入れていました。

しかし、ADF4110の基準波のスルーレート(波形が立ち上がる時間)がXXV/uS以上でなくてはいけません。周波数が低くなるほど、この値は厳しくなります。

一方、DDSの出力はサイン波ですので、当然緩慢な立ち上がりです。そこで、もう一段DDS出力をアンプして、波形を3VPPくらいまで大きくし、高速コンパレータで整形したりしたのですが、あまり改善はありませんでした。

アナログデバイスのフォーラムなどで、検索していくと、どうもこのICでは10MHz以下の基準周波数では、使い物にならないらしいということが話題になっていたものがありました。試しに、デジタル回路用の20MHz台のクロックICで作った波形を入れると、何とも清んだいい波形(音)が得られました。

まあ、DDSのTCXOをあきらめ、普通のクリスタルで基準周波数を上げれば済むことですが、このころTC9256Pの存在がわかり、こちらは逆に「4.5MHzが標準値」ということで、ICを変更した経緯があります。

|